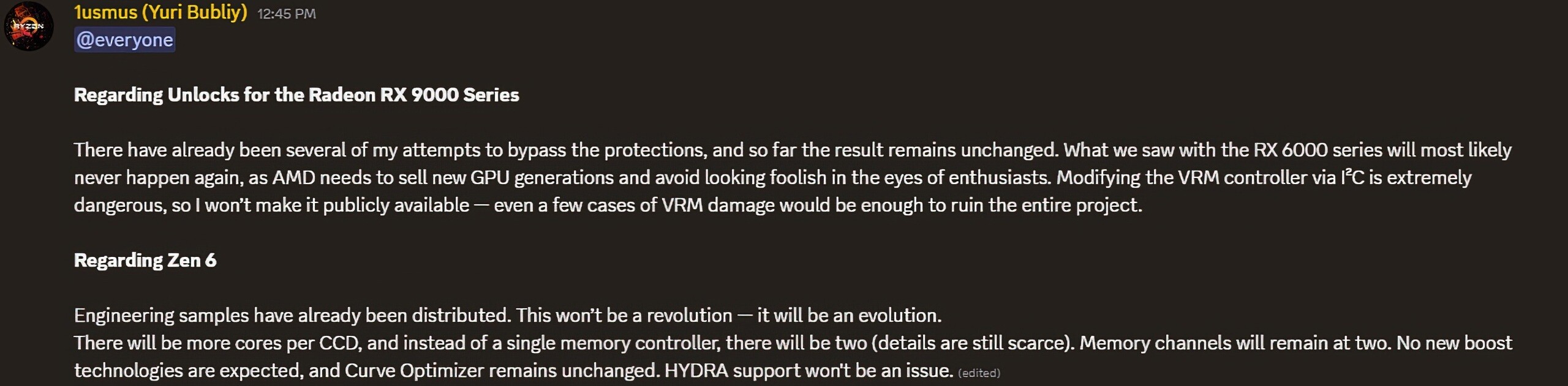

According to reports, AMD is currently distributing samples of its upcoming Ryzen desktop processor, which will be powered by the "Zen 6" microarchitecture and is codenamed "Medusa Ridge," to key industry partners like platform designers and OEMs. This information comes from Yuri Bubliy, also known as 1usmus, who is the creator of the Hydra tuning software and the now-retired DRAM Calculator for Ryzen. The new processor will feature updates to both the CCDs and client I/O die, as confirmed by AMD.

AMD has revealed that the "Zen 6" CCD will be manufactured on the TSMC N2 (2 nm) node, which has already entered risk production earlier this year. Mass production of 2 nm chips is expected to begin later in the year. This new node offers a significant increase in transistor densities compared to the current TSMC N4P node used for the 8-core "Zen 5" CCD. Sources suggest that AMD may increase core counts per CCD to 12 and provide the CCD with 48 MB of L3 cache.

It is unclear whether the 12 cores will be arranged in a single CCX with 48 MB L3 cache or if there will be a dual-CCX layout with 6 cores per CCX sharing 24 MB of L3 cache each. Another major upgrade with "Medusa Ridge" is the client I/O die (cIOD), which is expected to be built on a newer EUV node like 5 nm N5 or 4 nm N4P, a significant improvement from the current 6 nm N6. The main reason for updating the cIOD is to enhance the memory controller architecture.

AMD is planning to introduce a new dual memory controller architecture with "Medusa Point," which will still have two DDR5 channels per socket but redesigned for higher memory speeds to compete with Intel in this aspect. While there are no expected updates to CPU frequency boosting technologies like PBO and Curve Optimizer, 1usmus believes that Hydra support should be relatively straightforward.