Cerabyte's Revolutionary Ceramic Nano Memory Storage System

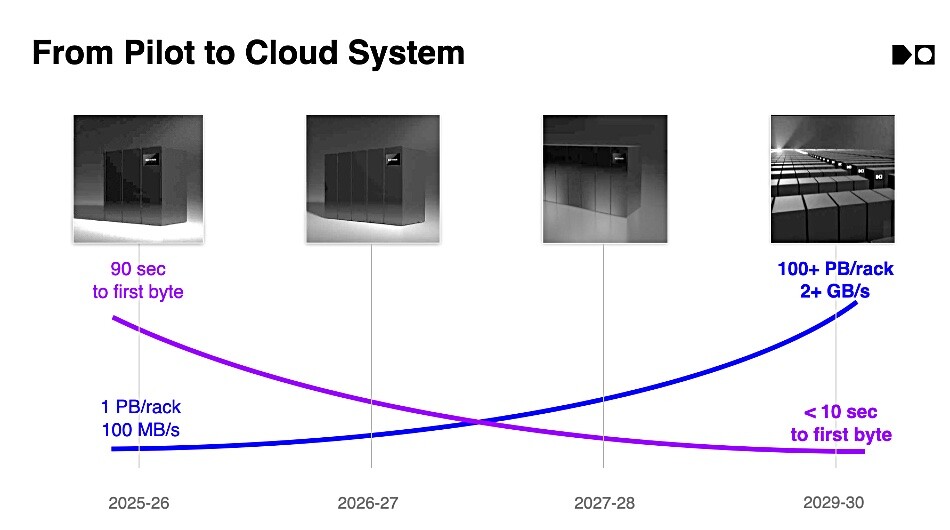

Cerabyte has recently revealed an extensive plan for its Ceramic Nano Memory archival storage system, which is set to become a cloud-based platform capable of storing over 100 PB per rack by the year 2030. The company anticipates that data transfer speeds will surpass 2 GB/s, with the time to first byte dropping below 10 seconds. This marks a significant improvement over its current pilot system, which currently only delivers 1 GB per rack, 100 MB/s throughput, and a 90-second access time.

The initial pilot phase, scheduled to run until 2026, will validate the 1 PB per rack design. A mid-cycle refresh around 2027-2028 aims to increase rack density to the double-digit petabyte range, halve access times, and more than double throughput. By 2029-2030, Cerabyte aims to achieve its full 100 PB capacity, maintain transfer rates exceeding 2 GB/s, and reduce access latency to under 10 seconds.

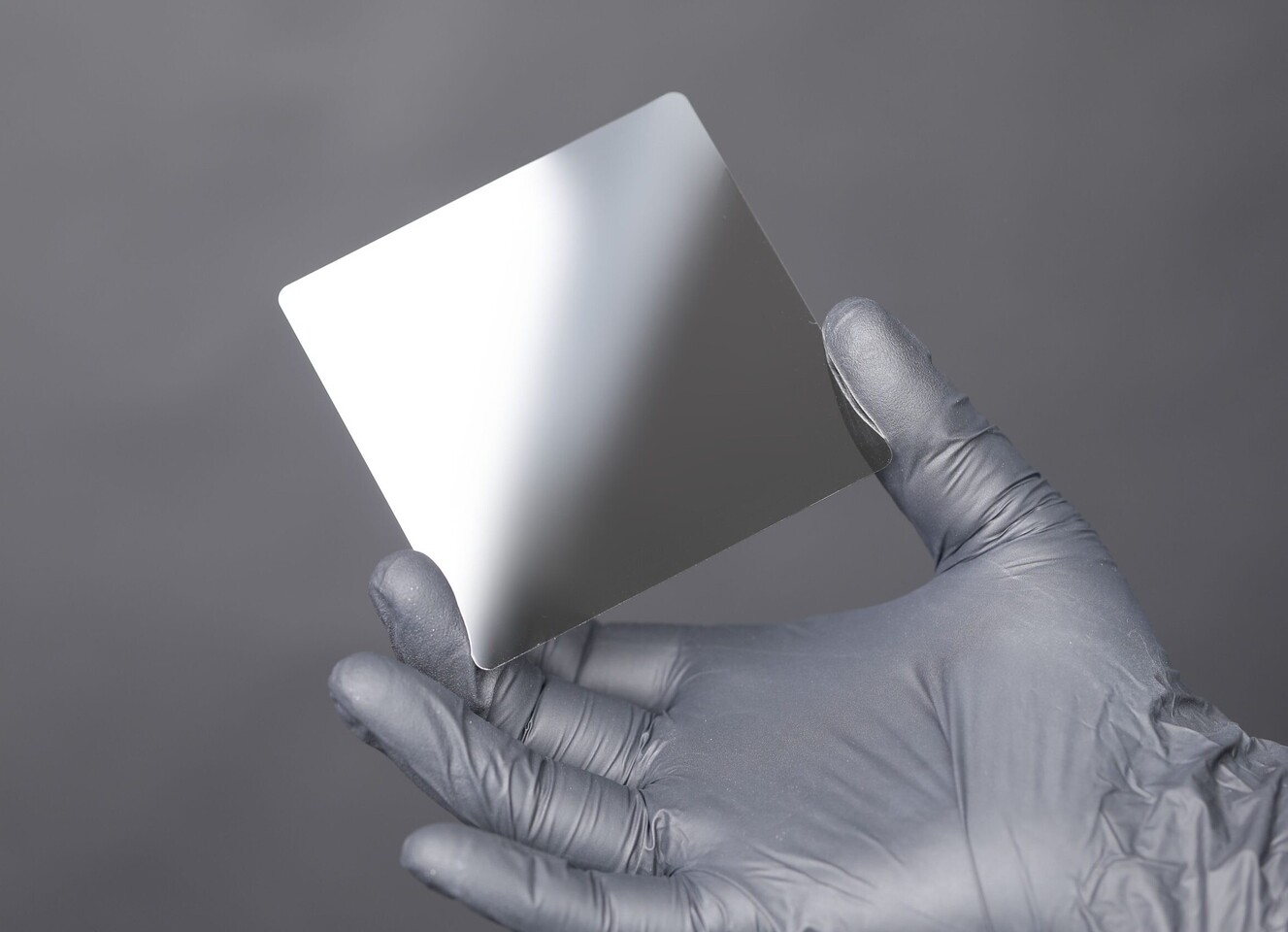

Cerabyte's innovative approach involves using 100 µm-thin glass panels coated with a 10 nm ceramic film. Data is inscribed by etching microscopic holes in the ceramic layer using a femtosecond laser, creating patterns that can be read by a high-resolution camera.

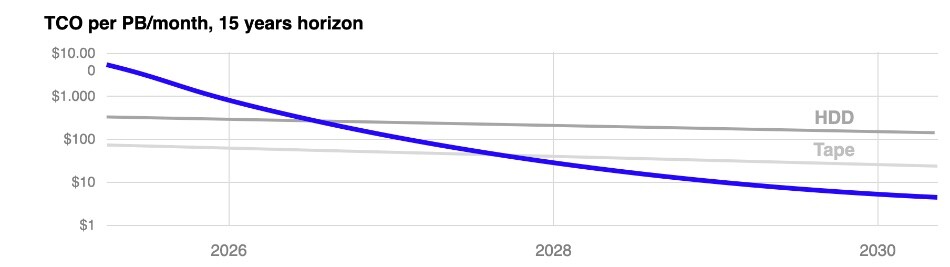

Multiple 9x9 cm tablets can fit into cartridges similar in size to magnetic tape, with robotic arms handling all media swapping. Financially, Cerabyte projects that the total cost of ownership will decrease from approximately $7,000-$8,000 per PB-month today to just $6-$8 per PB-month by 2030. The company has received support from Pure Storage, Western Digital, In-Q-Tel, and the European Innovation Council's Accelerator fund. So far, the startup has secured around $10 million in seed financing, along with over $4 million in grants.

Compared to traditional tape libraries, Cerabyte's system offers at least twice the bandwidth, a lifespan exceeding 100 years (compared to tape's 7-15 years), and half the cost per terabyte. Additionally, the company plans to adopt helium-ion beam writing by 2045 to reduce bit sizes from approximately 300 nm to 3 nm, potentially increasing per-rack capacity into the exabyte range.